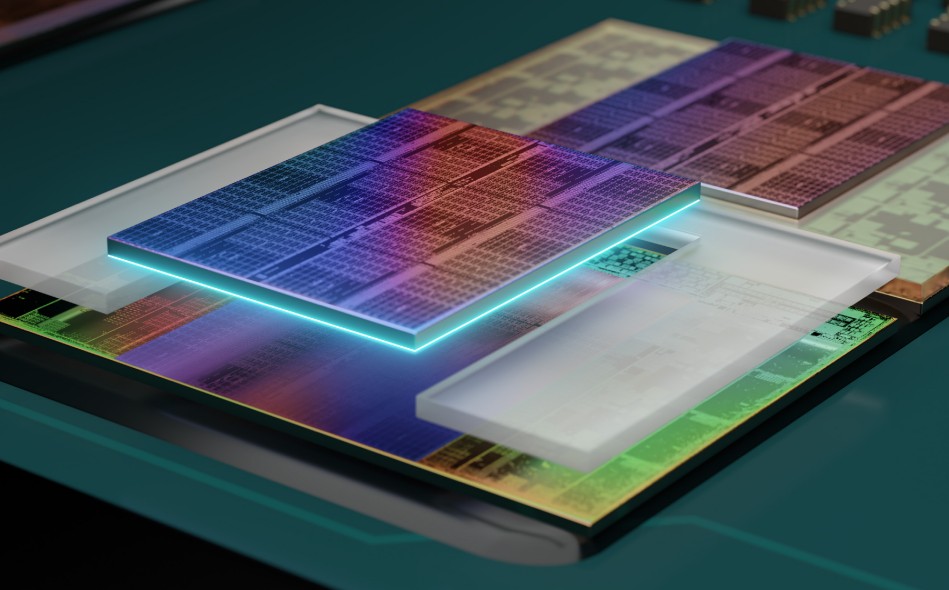

International Solid-State Circuits Konferansı çevrimiçi olarak gerçekleşiyor ve AMD, 3D V-Cache tasarımının bazı ayrıntılarını paylaştı. Burada 3D V-Cache’in genel tasarımının yanı sıra dahil edilen önbellek yongalarının CPU silikonuyla nasıl bir araya geldiği gösteriliyor.

Önbellek yongasının 41 mm² boyutunda olduğunu görüyoruz ve Through Silicon Via (TSV) bağlantılarıyla birlikte doğrudan L3 önbellek ile bir bağlantı sağlanıyor. AMD, tüm CPU çekirdeklerinin 3D V-Cache ile iletişim kurabilmesi için L3 düzeyinde paylaşılan bir halka veri yolu (ring bus) tasarımı uyguladı. L3 önbelleğinin tamamının, performansın daha da artmasını sağlamak amacıyla her bir çekirdek için kullanılabilir olduğu söyleniyor.

3D V-Cache, CCX ve 3D yonga arasında toplamda 8.192 bağlantı için tek bir CPU çekirdeği ile 1.024 temas arabirimine sahip birden çok 8 MB’lık “birimden” oluşuyor. Bu da tam çift yönlü modda dilim başına saniyede iki terabaytı aşan bir bant genişliğine izin veriyor. CCX’in entegre bir parçası olmamasına rağmen, 3D V-Cache için tam L3 hızları sunulabilecek.

AMD’nin ayrıca yaklaşmakta olan Ryzen 7 5800X3D için CCX’inin tasarımını geliştirdiği, güç tüketimini azalttığı ve frekans hızlarını iyileştirmek için çeşitli iyileştirmeler yaptığı söyleniyor. Şirket Ryzen 7 5800X3D için henüz bir lansman tarihi açıklamadı. 3D V-Cache ve çeşitli küçük optimizasyonlarla gelen yongaların Intel Alder Lake ile rekabet edip edemeyeceğini zamanla göreceğiz. Nitekim kırmızı takım Zen 4 mimarili işlemcilerini yine bu yıl piyasaya sürecek.

3D V-Cache için kullanılan ek SRAM, N7 işleminde TSMC tarafından üretiliyor. AMD, slaytlarda bu çözümünden 64 MB L3 önbellek söyleminin yanı sıra “genişletilmiş L3 Cache” olarak bahsediyor. 3D V-Cache SRAM 41 mm2 boyutunda ve termal yayılıma yardımcı olmak için CCD üzerinde bazı geliştirmeler yapıldı. Kırmızı takım ayrıca her şeyi önceki nesil CPU’larla aynı pakete sığdırabilmek için CCD’leri ve L3 önbelleğini inceltmek zorunda kaldı.